# JPEGエンコーダ・ハードウェアIP

神奈川工科大学大学院 信号処理応用研究室

当研究室HPにて、JPEGエンコーダ回路を公開中

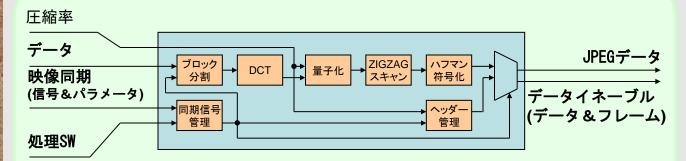

映像用同期信号形式(垂直・水平・データ)による入力に特化したJPEGエンコーダ・ハードウェアIPです。複雑な入力制御・コア制御を撤廃した為、JPEGの構造を理解する必要なく、短時間でコアを組み込む事ができます。

## **JPEGエンコーダ回路**

ほぼ無劣化の画質優先からファイルサイズ 10分の1以上の圧縮優先まで自由自在!!

(圧縮率0~64の65パラーメータを1枚1枚に設定可能)

## 単純明快な4種類の信号がコアを制御!!

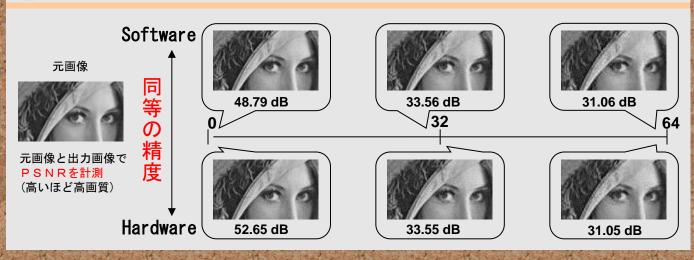

#### 圧縮率と画質

- ・簡単に使えるJPEGエンコーダIPですが、精度は市販品にも劣りません!

- ・低~高圧縮率まで、一般的なソフトウェアと比較してもほぼ同程度の画質と圧縮率を実現しています。

- ・引き続き、画質や圧縮効率の向上などの最適化を行いながら開発中です。

## 動作確認

### **JPEG仕様**

・<u>符号化形式</u> :基本DCT方式(ノンプログレッシブ方式)

• <u>JEPG形式</u> : JFIFフォーマット

ハフマン形式 : ハフマンテーブル2面 (輝度・色差: ITU-T勧告T.81を使用)

・<u>量子化形式</u>:量子化テーブル2面(輝度・色差: ITU-T勧告T.81を基準に指定倍率をかけて使用)

•画像形式 : YCbCr = 4:4:4 , ノンインタリーブ方式(スキャンセグメント3枚)

#### **一**回路仕様

#### 全て単一クロックによる同期設計

・ 入力形式:映像同期信号形式(垂直・水平・データ)

8bitバイナリデータ(カラーは成分ごとに3フレーム分で入力)

VESA規格の他、一定範囲内であれば独自の同期信号パラーメータを設定可能

・出力形式:フレームイネーブル・データイネーブル・16bitバイナリデータ

- <u>回路規模</u>: 1. Vertex6(Slice:約3500 Mult:27個 36K\_BlockRAM: 20個) @ Xilinx ML605

2. Spartan3A-DSP(Slice:約7000 Mult:27個 18K\_BlockRAM:40個) @ TED TB-3S-3400DSP-IMG

3. Arria II GX OK

(※周辺回路により合成結果は異なります)

• <u>最大動作周波数</u>: 1. 162MHz 以上 2. 85MHz 以上 3. 未計測

・<u>最大解像度</u>:2560×1920(※ただし8の倍数解像度に限る。実機動作はDVI入力より1920×1200まで確認)

・<u>フレームレート</u>:最大動作周波数内で入力するクロックの周波数、同期信号パラーメータによって変動

(例 VESA規格: [SVGA @ 60fps : 40Mhz], [XGA @ 60fps : 65Mhz])

( モノクロ:上記条件 fps , カラー:モノクロの3分の1 fps )

### グナモ

### 連絡先

#### 神奈川工科大学 信号処理応用研究室

〒243-0292 神奈川県厚木市下荻野1030 URL:http://www.ess.ic.kanagawa-it.ac.jp/ TEL:046 (242) 0030 (内線:6061)

共同研究先:株式会社 マイクロ・テクニカ

http://www.microtechnica.co.jp/