【VHDL による TCP/IP スタック コア】

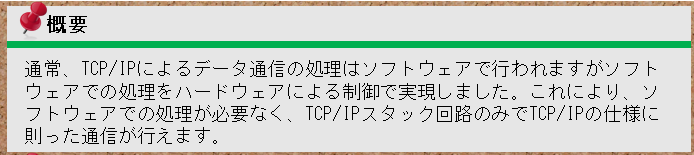

FPGA によるフルハードウェア化された TCP/IP 回路です.

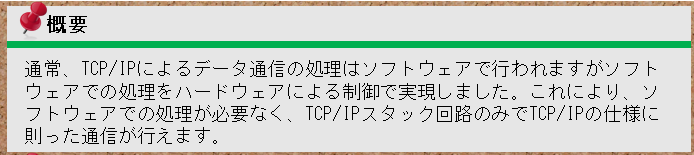

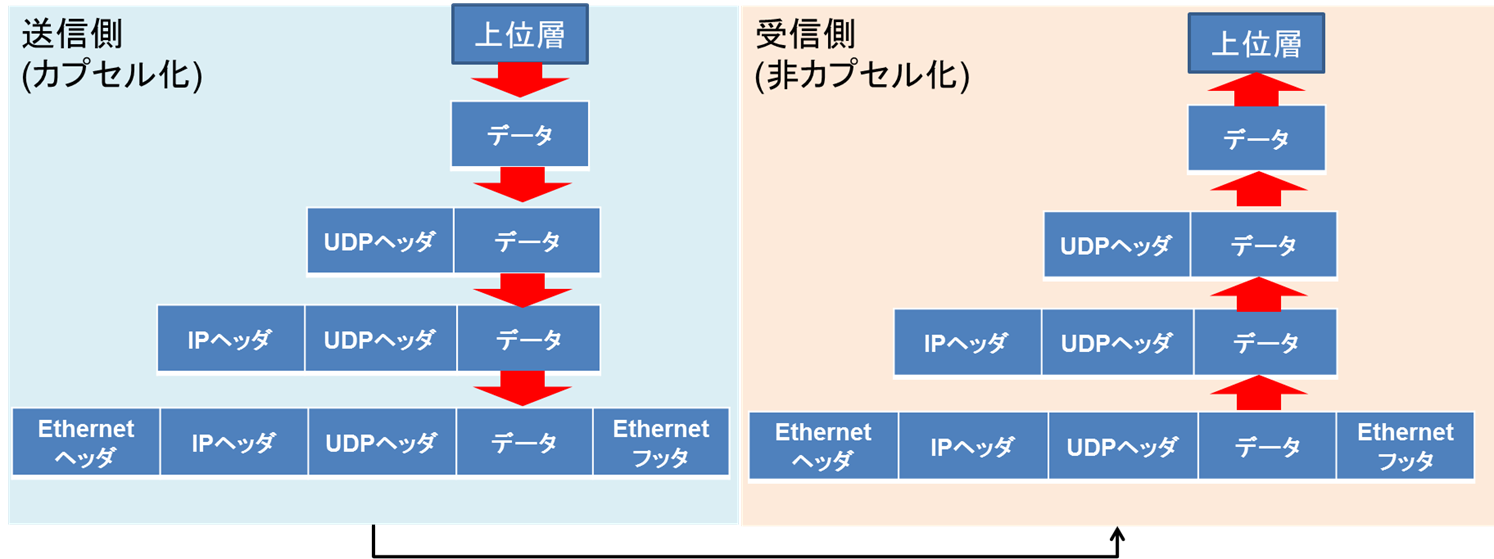

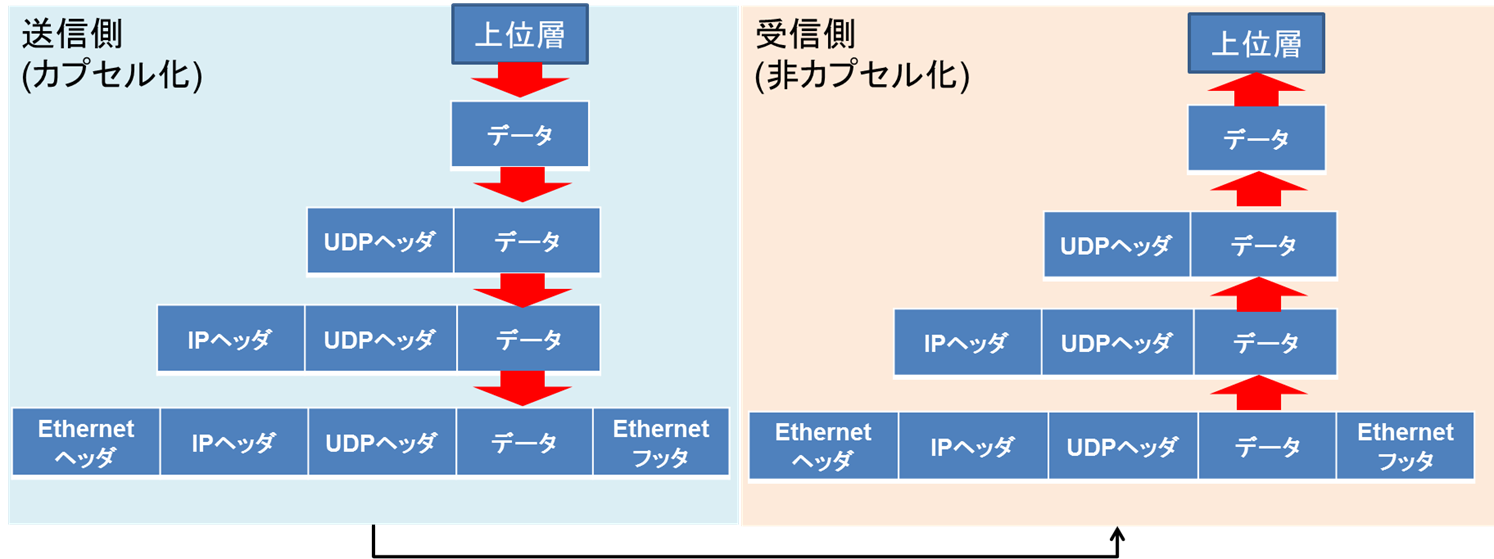

通常 TCP/IP 通信をする際,送信側,受信側共にデータに対しヘッダ情報が付加される.

このヘッダ情報はソフトウェアによって付加されるため,CPUパワーを使うことになり,

大量のデータのやり取りにCPUが不可欠となります.

CPUが不可欠ということは,それに伴うソフトウェアも必要となります.

よって,CPUが不要なシステムがあれば,コスト,開発期間などのメリットが生まれます!

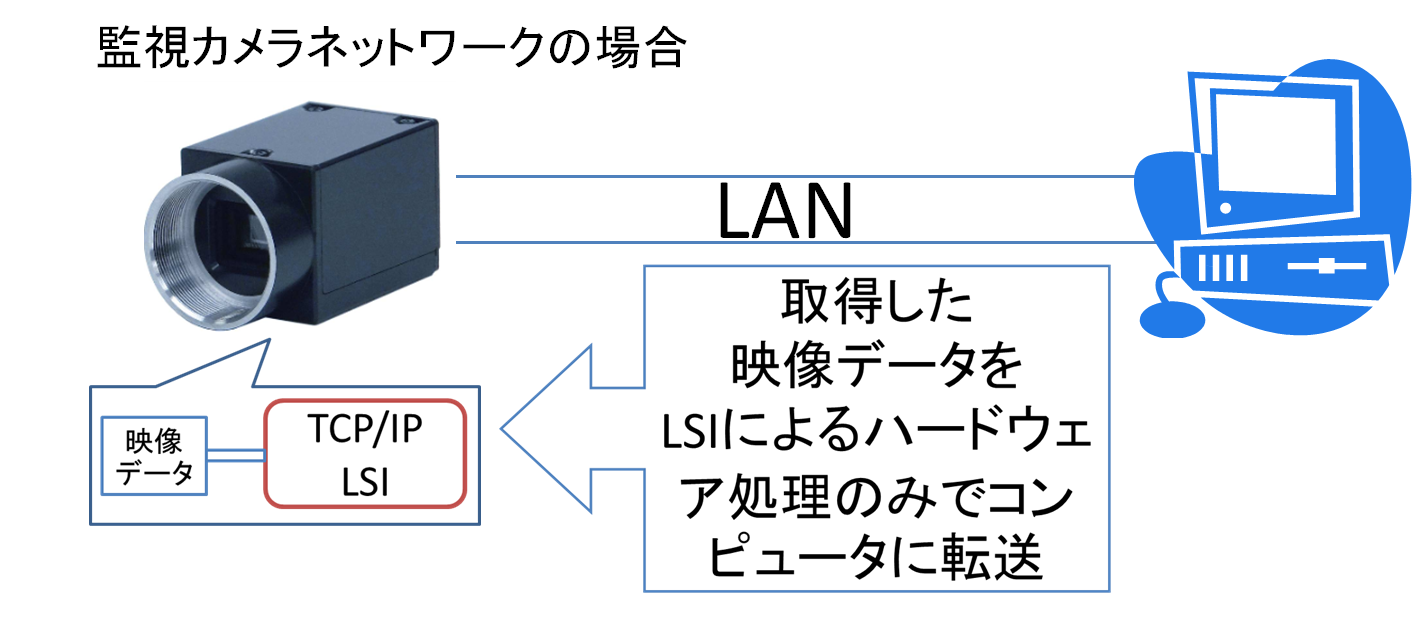

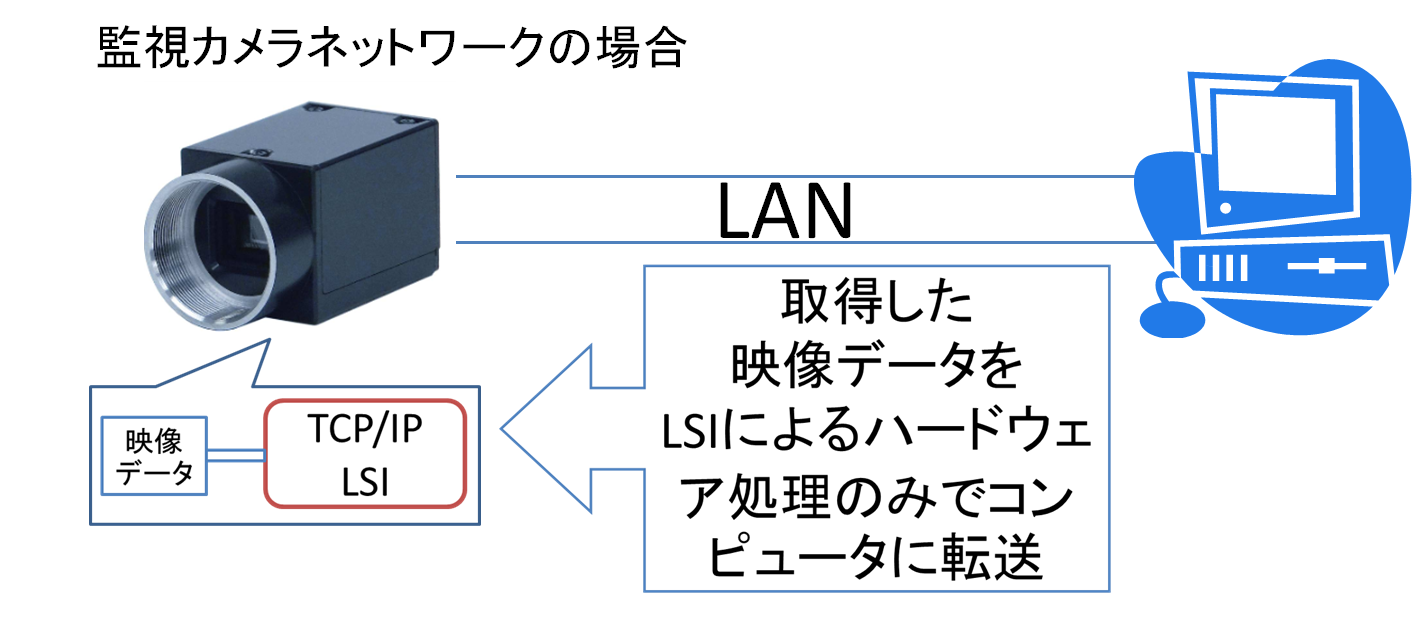

例えば・・・・・

イメージセンサの出力を TCP/IP スタック回路に接続すれば,映像データはそのまま LAN 上を流れます.

ソフトウェアが介在しないため,柔軟性には欠ける部分がありますが,固定した用途には十分です!!

【現在の状況】

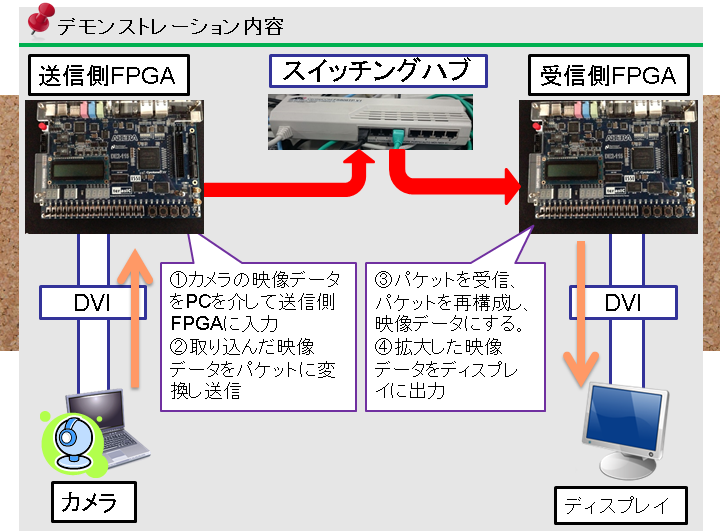

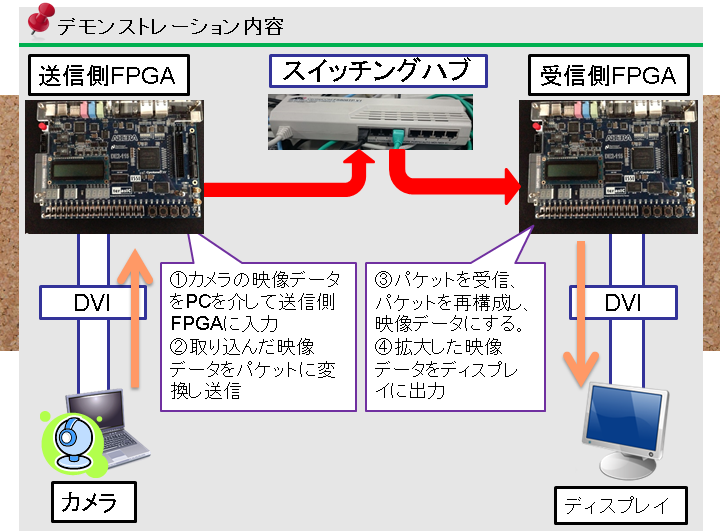

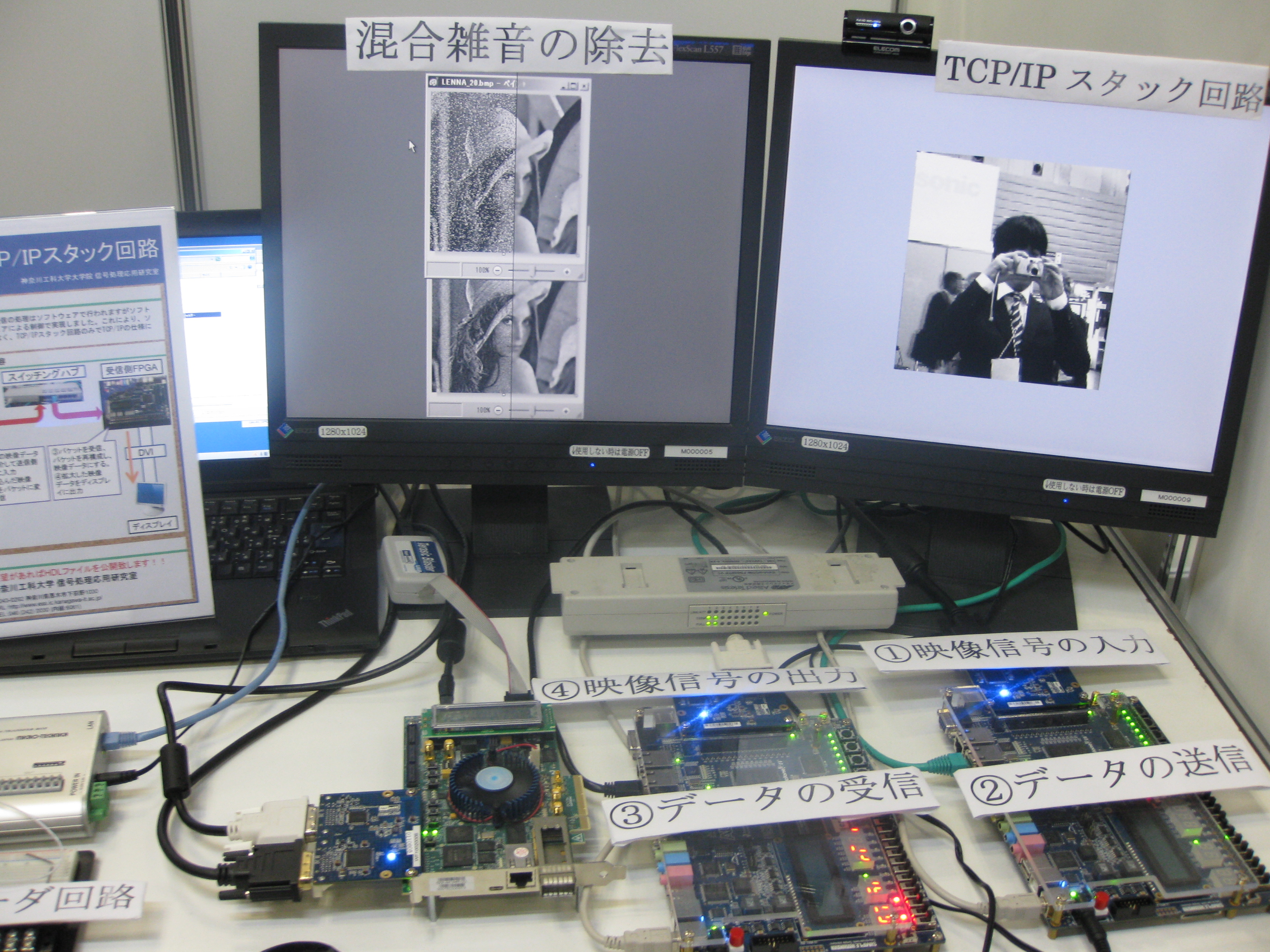

組込み総合技術展 ET2014 においてデモを実施!

【実際の会場でのデモの様子】

ご要望があれば HDL コードを公開致します.

★なお技術的な事柄についての質問などは一切受け付けておりませんので,予めご了承下さい.

(c) SPA Lab 2014